# Node and Label Placement in a Layered Layout Algorithm

John Julian Carstens

Master Thesis September 2012

Christian-Albrechts-Universität zu Kiel Real-Time and Embedded Systems Group Prof. Dr. Reinhard von Hanxleden

Advised by Dipl.-Inf. Christoph Daniel Schulze

# Abstract

In graphical modelling, the arrangement of diagram elements can be a tiresome and mechanic work. To free users from this, layout algorithms arrange the diagram elements automatically.

Different modelling domains require different layouts. A layout approach suitable for data flow diagrams is the layered layout approach. This approach is structured in several phases, of which one is called node placement. Present implementations are known to produce many edge bends. One task of this thesis is to employ a node placement algorithm which yields significantly less edge bends.

Another well known problem in layout algorithms is label placement. Present approaches rely on a post-processing by placing labels after the diagram has been laid out. The approaches presented in this thesis integrate label placement into the layout, resulting in more freedom and clean placements of labels.

Evaluation shows that both tasks can be fulfilled, but have to accept a trade-off which is a generally larger drawing of the respective diagrams.

## Eidesstattliche Erklärung

Hiermit erkläre ich an Eides statt, dass ich die vorliegende Arbeit selbstständig verfasst und keine anderen als die angegebenen Quellen und Hilfsmittel verwendet habe.

Kiel,

# Contents

| 1 | Intr | oductio  | on la            | 1  |

|---|------|----------|------------------------------------------------------|----|

|   | 1.1  | Relate   | ed Work                                              | 3  |

|   | 1.2  | Reseat   | rch Goals                                            | 6  |

|   |      | 1.2.1    | Improving Node Placement                             | 6  |

|   |      | 1.2.2    | Implementing Label Placement                         | 7  |

|   | 1.3  | Overv    | <i>r</i> iew                                         | 8  |

| 2 | Prel | iminar   | ies                                                  | 9  |

|   | 2.1  | Termi    | nology and Definitions                               | 9  |

|   | 2.2  |          | ntegrated Environment for Layout Eclipse Rich Client | 12 |

|   |      | 2.2.1    | KIELER Infrastructure for Meta Layout                | 13 |

|   | 2.3  | The L    | ayered Layout Approach                               | 14 |

|   | 2.4  |          | Layered                                              | 16 |

|   |      | 2.4.1    | The Five Phases of KLay Layered                      | 16 |

|   |      | 2.4.2    | Intermediate Processors                              | 20 |

| 3 | Nod  | le Place | ement                                                | 23 |

| - | 3.1  |          | em Statement                                         | 23 |

|   | 3.2  |          | oach                                                 | 28 |

|   |      | 3.2.1    | The approach of Brandes and Köpf                     | 28 |

|   |      | 3.2.2    | Introducing vertex size and ports                    | 41 |

|   |      | 3.2.3    | Balancing and fault tolerance                        | 46 |

|   | 3.3  |          | mentation                                            | 48 |

|   |      | 3.3.1    | Implementation in the context of KLay Layered        | 49 |

|   |      | 3.3.2    | Data structures                                      | 50 |

|   |      | 3.3.3    | Support for complex structures                       | 51 |

|   |      | 3.3.4    | Handling of type 2 conflicts                         | 53 |

|   |      | 3.3.5    | Steps to a node placement choice                     | 53 |

|   | 3.4  | Evalu    |                                                      | 54 |

|   |      | 3.4.1    | Evaluation metrics                                   | 55 |

|   |      | 3.4.2    | Evaluation models                                    | 58 |

|   |      | 3.4.3    | Evaluation results                                   | 59 |

|   |      |          |                                                      |    |

Contents

| Lab              | el Place                                                                                    | ement 67                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 4.1              | Proble                                                                                      | em Statement                                                                                                                                                                                                                                                                                                                                                                                                                                           | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

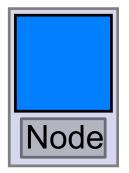

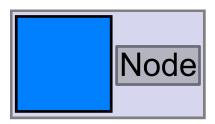

|                  | 4.1.1                                                                                       | Node Label Placement                                                                                                                                                                                                                                                                                                                                                                                                                                   | l                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                  | 4.1.2                                                                                       | Port Label Placement                                                                                                                                                                                                                                                                                                                                                                                                                                   | )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                  | 4.1.3                                                                                       | Edge Label Placement                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                  | 4.1.4                                                                                       | Introducing Side Aware Edge Label Placement                                                                                                                                                                                                                                                                                                                                                                                                            | ŀ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                  | 4.1.5                                                                                       | On the complexity of SAELP                                                                                                                                                                                                                                                                                                                                                                                                                             | ;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 4.2              | Appro                                                                                       | oach                                                                                                                                                                                                                                                                                                                                                                                                                                                   | )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                  | 4.2.1                                                                                       | Spicing up layout with label placement                                                                                                                                                                                                                                                                                                                                                                                                                 | )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                  | 4.2.2                                                                                       | Node Labels and Node Margins                                                                                                                                                                                                                                                                                                                                                                                                                           | )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                  | 4.2.3                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                  | 4.2.4                                                                                       | Edge Labels                                                                                                                                                                                                                                                                                                                                                                                                                                            | ;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 4.3              | Imple                                                                                       | mentation                                                                                                                                                                                                                                                                                                                                                                                                                                              | )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                  | 4.3.1                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                        | )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                  | 4.3.2                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                        | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                  | 4.3.3                                                                                       | -                                                                                                                                                                                                                                                                                                                                                                                                                                                      | )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                  | 4.3.4                                                                                       | 1,5,0,1                                                                                                                                                                                                                                                                                                                                                                                                                                                | )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                  | 4.3.5                                                                                       | End label placement                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                  | 4.3.6                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Ł                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 4.4              | Evalua                                                                                      | ation                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                  | 4.4.1                                                                                       | Example results                                                                                                                                                                                                                                                                                                                                                                                                                                        | <i>,</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|                  | 4.4.2                                                                                       | -                                                                                                                                                                                                                                                                                                                                                                                                                                                      | )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                  |                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| Con              |                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 5.1              |                                                                                             | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 5.2              | Future                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|                  | 5.2.1                                                                                       | Node Placement                                                                                                                                                                                                                                                                                                                                                                                                                                         | ;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                  | 5.2.2                                                                                       | Label Placement                                                                                                                                                                                                                                                                                                                                                                                                                                        | ;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| Bibliography 107 |                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|                  | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>Con<br/>5.1<br/>5.2</li> </ul> | <ul> <li>4.1 Problet</li> <li>4.1.1</li> <li>4.1.2</li> <li>4.1.3</li> <li>4.1.4</li> <li>4.1.5</li> <li>4.2 Approprise</li> <li>4.2.1</li> <li>4.2.2</li> <li>4.2.3</li> <li>4.2.4</li> <li>4.3 Implet</li> <li>4.3.1</li> <li>4.3.2</li> <li>4.3.3</li> <li>4.3.4</li> <li>4.3.5</li> <li>4.3.6</li> <li>4.4 Evalue</li> <li>4.4.1</li> <li>4.4.2</li> <li>Conclusion</li> <li>5.1 Summ</li> <li>5.2 Future</li> <li>5.2.1</li> <li>5.2.2</li> </ul> | 4.1.1       Node Label Placement       71         4.1.2       Port Label Placement       72         4.1.3       Edge Label Placement       73         4.1.4       Introducing Side Aware Edge Label Placement       74         4.1.5       On the complexity of SAELP       75         4.2       Approach       79         4.2.1       Spicing up layout with label placement       79         4.2.2       Node Labels and Node Margins       80         4.2.3       Port Labels       83         4.2.4       Edge Labels       83         4.2.4       Edge Labels       85         4.3       Implementation       90         4.3.1       Node size and margins       90         4.3.2       Port label space       91         4.3.3       Simplifying label placement       92         4.3.4       SAELP heuristics       92         4.3.5       End label placement       93         4.4       Evaluation       93         4.4       Evaluation       94         4.4       Evaluation of space usage       99         5.1       Summary       103         5.2       Future Work       104 <t< td=""></t<> |  |  |

# List of Figures

| 1.1  | A UML diagram showing the GoodRelations ontology                     | 2  |

|------|----------------------------------------------------------------------|----|

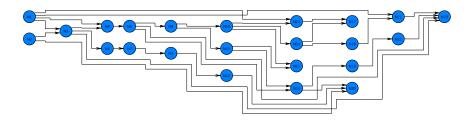

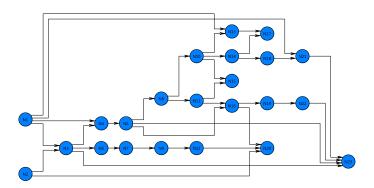

| 1.2  | A data flow diagram from the Ptolemy II modelling tool               | 3  |

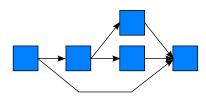

| 1.3  | A KLay Layered result with unnecessary edge bends                    | 7  |

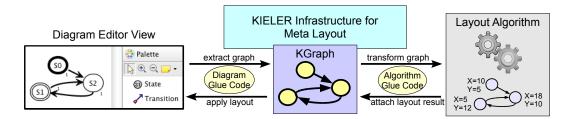

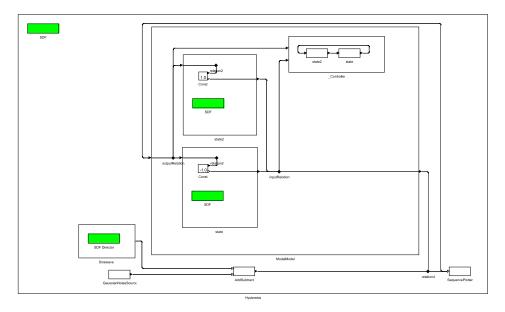

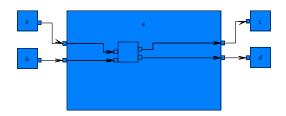

| 2.1  | KIML structure overview                                              | 13 |

| 2.2  | Balancing in the context of Sugiyama's aesthetics criteria           | 15 |

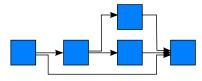

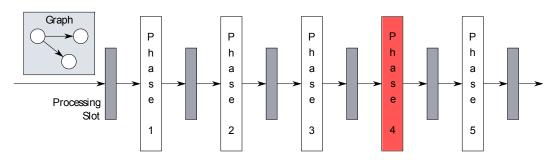

| 2.3  | An overview of the KLay Layered architecture                         | 16 |

| 2.4  | A simple example of cycle breaking                                   | 17 |

| 2.5  | A properly layered graph with inserted dummy vertices                | 18 |

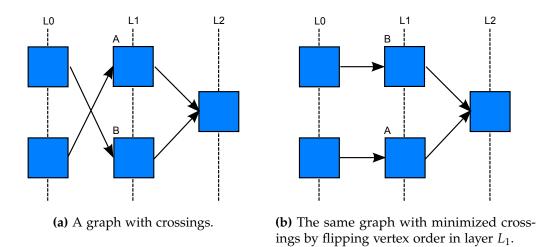

| 2.6  | An example of crossing minimization                                  | 18 |

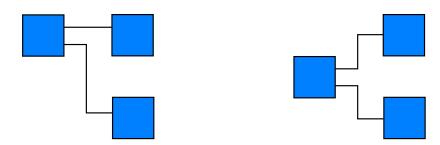

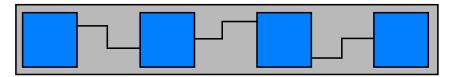

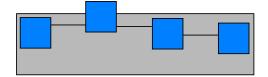

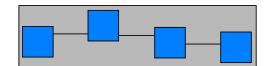

| 2.7  | The effects of different node placement methods                      | 19 |

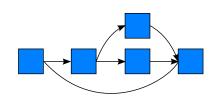

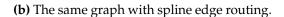

| 2.8  | Examples of different edge routing methods                           | 20 |

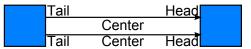

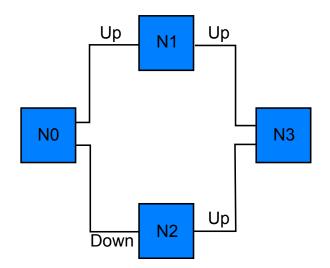

| 3.1  | The node placement phase in KLay Layered                             | 24 |

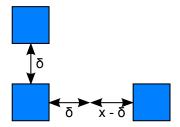

| 3.2  | The minimum separation constraint                                    | 24 |

| 3.3  | The effects of different node placements                             | 25 |

| 3.4  | Aesthetics criteria influenced by node placement                     | 26 |

| 3.5  | Balancing and edge bends                                             | 27 |

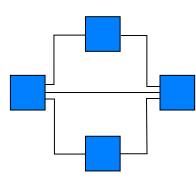

| 3.6  | Three different conflict types                                       | 30 |

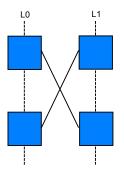

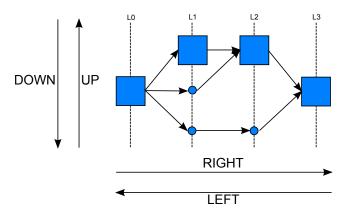

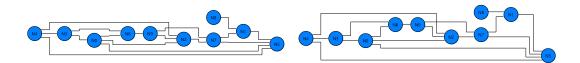

| 3.7  | Iteration directions                                                 | 31 |

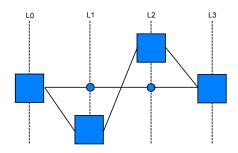

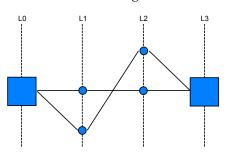

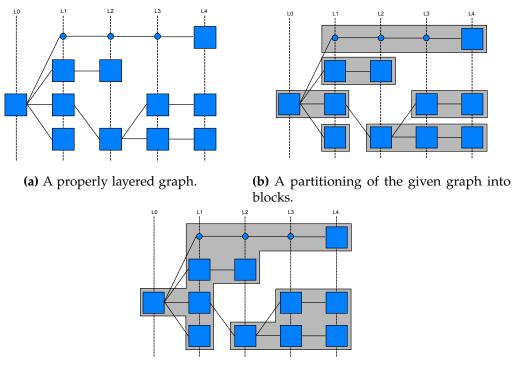

| 3.8  | Different partitionings of a graph                                   | 32 |

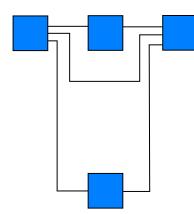

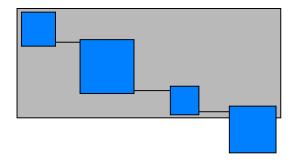

| 3.9  | The effect of balancing                                              | 41 |

| 3.10 | Port positions and edge bends                                        | 41 |

| 3.11 | Naive approach to vertex size handling                               | 43 |

| 3.12 | Post shift effects                                                   | 45 |

| 3.13 | A nested graph with large vertices                                   | 47 |

| 3.14 | Layout options for KLay Layered                                      | 49 |

| 3.15 | Class diagram of the BKAlignedLayout class                           | 50 |

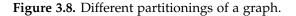

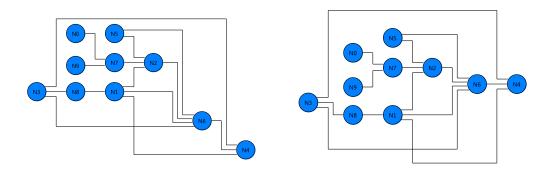

| 3.16 | Different hierarchy levels in a graph                                | 51 |

| 3.17 | Edge compaction using an edge spacing factor                         | 52 |

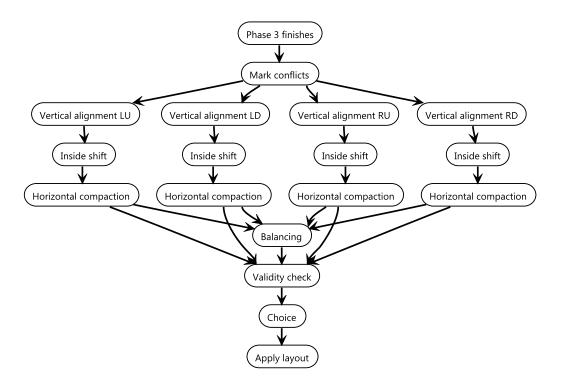

| 3.18 | Process of phase four with the new node placer                       | 54 |

| 3.19 | A graph with different algorithms used for node placement $\ldots$ . | 56 |

## List of Figures

| 3.20 | A Ptolemy II diagram with different algorithms used for node place-   |     |

|------|-----------------------------------------------------------------------|-----|

|      | ment                                                                  | 57  |

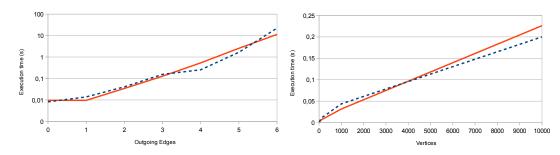

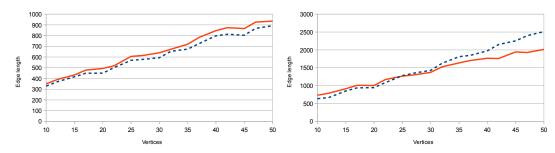

| 3.21 | Performance comparison of two node placers                            | 63  |

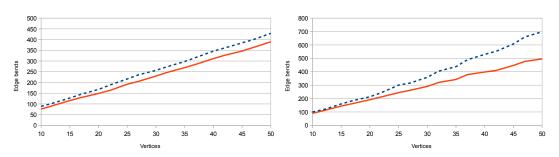

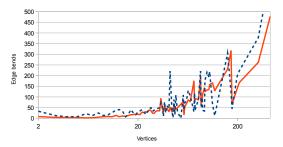

| 3.22 | The edge bend metric in the different model sets                      | 64  |

| 3.23 | The edge length metric in the different model sets                    | 65  |

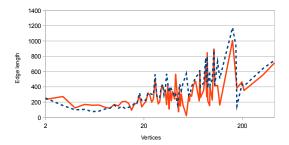

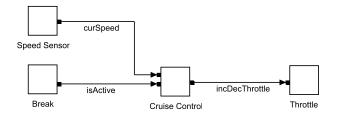

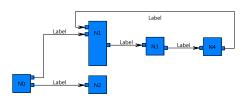

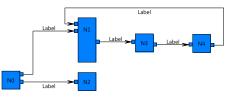

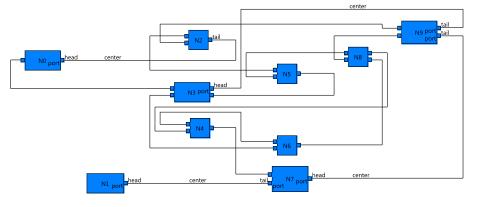

| 4.1  | A simple data flow diagram with labels                                | 68  |

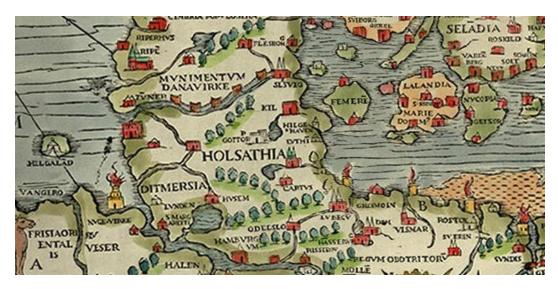

| 4.2  | An excerpt of the Carta Marina                                        | 68  |

| 4.3  | Equivalent structures in cartography and graph drawing                | 70  |

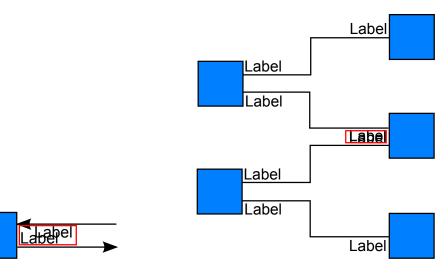

| 4.4  | Possible reductions of the label position set                         | 71  |

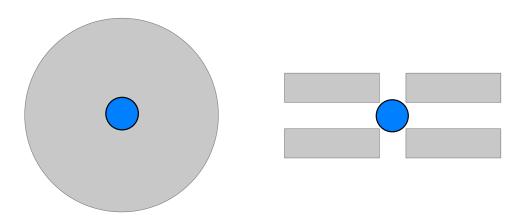

| 4.5  | Placement areas of a port, a vertex, and an edge                      | 72  |

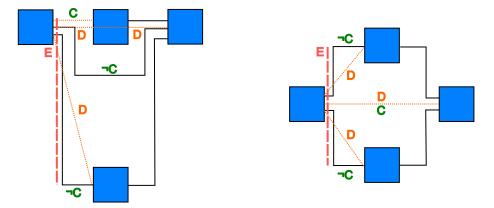

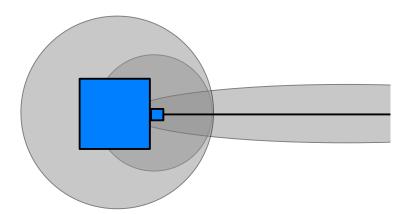

| 4.6  | Placement areas of the different edge label types                     | 74  |

| 4.7  | Ambiguous edge label placement                                        | 74  |

| 4.8  | Ambiguity due to side choice in label placement                       | 75  |

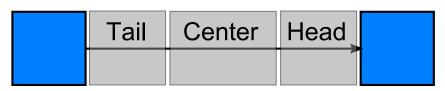

| 4.9  | Six discrete positions for the three labels of an edge                | 77  |

| 4.10 | Improved readability via reserving space                              | 79  |

| 4.11 | Label placement inside a vertex                                       | 81  |

| 4.12 | Node labels and margins                                               | 82  |

|      | Possible placements when all sides of the vertex are blocked by edges | 82  |

| 4.14 | Stretching the edge to introduce enough space for the port label      | 83  |

| 4.15 | Reserving edge label candidate positions for port labels              | 83  |

| 4.16 | Placing port labels inside of vertices                                | 84  |

|      | Port label placement inside of the port itself                        | 84  |

| 4.18 | End label space is kept clear via vertex margins                      | 85  |

|      | Dummy vertices for center label placement                             | 86  |

| 4.20 | Swapping label dummy vertices                                         | 86  |

|      | Examples for the three SAELP approaches                               | 87  |

|      | Overlap in a direction-based label side choice                        | 88  |

|      | Overlaps in a greedy approach                                         | 88  |

|      | Example for the greedy SAELP heuristic                                | 89  |

|      | Possible conflict in a SAELP heuristic                                | 89  |

|      | Edge label placement in a portless graph                              | 96  |

|      | Problems of ambiguity on vertices with more than two edges            | 97  |

|      | Port-based graph with two different port label placements             | 98  |

|      |                                                                       | 100 |

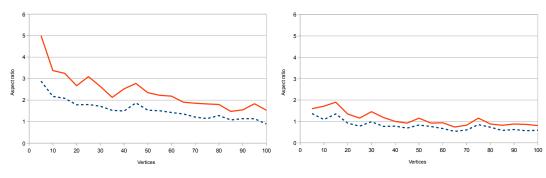

|      | Aspect ratio with and without label placement                         |     |

|      | 1 I                                                                   |     |

# List of Tables

| 3.1  | Aesthetics criteria influenced by node placement                          | 25  |

|------|---------------------------------------------------------------------------|-----|

| 3.2  | Variables used in the mark conflicts algorithm                            | 34  |

| 3.3  | Properties of the evaluation model sets                                   | 59  |

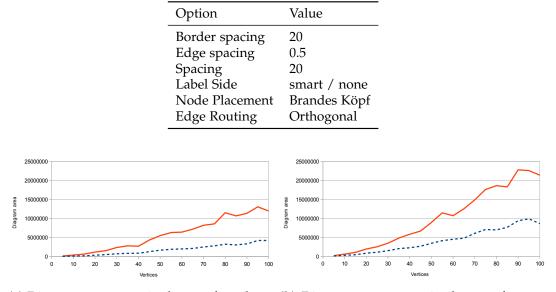

| 3.4  | Layout options chosen for evaluation                                      | 59  |

| 3.5  | The results of the evaluation of the portless model set                   | 60  |

| 3.6  | The results of the evaluation of the port-based model set                 | 60  |

| 3.7  | The results of the evaluation of the Ptolemy II model set $\ldots \ldots$ | 61  |

|      |                                                                           |     |

| 4.1  | The NodeLabelSizeAdjuster intermediate processor                          | 91  |

| 4.2  | The NodeMarginCalculator intermediate processor                           | 91  |

| 4.3  | The NodeLabelPlacer intermediate processor                                | 92  |

| 4.4  | The LabelSideSelector intermediate processor                              | 93  |

| 4.5  | The EndLabelProcessor intermediate processor                              | 94  |

| 4.6  | The LabelDummyInserter intermediate processor                             | 94  |

| 4.7  | The LabelDummySwitcher intermediate processor                             | 95  |

| 4.8  | The LabelDummyRemover intermediate processor                              | 95  |

| 4.9  | Properties of the evaluation model sets                                   | 99  |

| 4.10 | Layout options chosen for evaluation                                      | 100 |

|      |                                                                           |     |

# Abbreviations

- DAELP Discrete Admissible Edge Label Placement

- **GMF** Graphical Modelling Framework

- KAOM KIELER Actor-Oriented Modelling

- KIELER Kiel Integrated Environment for Layout Eclipse Rich Client

- **KIML** KIELER Infrastructure for Meta Layout

- KLay KIELER Layout Algorithms

- **OGDF** Open Graph Drawing Framework

- SAELP Side Aware Edge Label Placement

- UML Unified Modelling Language

# Introduction

A difficult problem with computer systems is to make them accessible and usable to a large group of users. Especially the different knowledge background and the experience of users in working with computer programs often poses a great hurdle to developing usable designs. Here, a compromise is found by abstracting the task in a way which allows many users to work in an environment that is already known to them. To achieve that, graphical modelling and design may be a feasible solution. A graphical web site editor is considered more usable than an editor which relies on textual source code.

The same holds for engineering and the design of large and complex systems. Here, popular abstraction is to combine the used hardware or software components graphically, rather than using a textual programming or hardware description language.

But building on a common abstraction is far from being the only benefit of graphical modelling. Beside its usage in design and development, graphical models can also be used for documenting and describing existing systems. An example for that are some model types of the Unified Modelling Language (UML). Class diagrams, for example, can describe large object oriented software in a way that allows a quicker overview compared to studying the source code line by line.

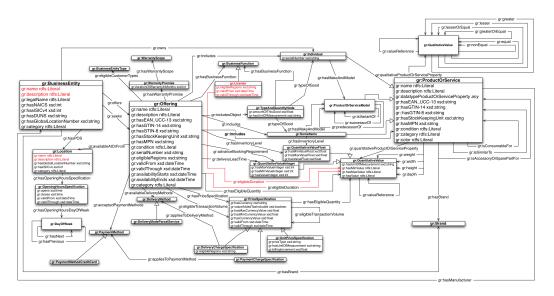

When comparing textual and graphical design, a core problem of graphical design appears: while layout and arrangement in a textual environment is typically straightforward due to the few levels of freedom, layout and arrangement in a graphical environment can be a complex and time-consuming problem. When designing a diagram such as the one shown in Figure 1.1, a lot of time is used to arrange the diagram elements, a task that usually results in no semantic benefit and may drive users away from graphical design due to its monotony.

Automatic layout algorithms were developed to alleviate users from the need of having to layout their diagrams manually. With that, diagrams can be arranged automatically, to free the user of this time-consuming and annoying task. As one can easily imagine, the automatic layout of diagrams is a demanding problem which

### 1. Introduction

**Figure 1.1.** An UML diagram showing the structure and relations of the GoodRelations ontology.<sup>1</sup>

offers an almost infinite pool of possible approaches. Each of these approaches usually focusses on a certain diagram type or class of diagram types, because the requirements to an automatic layout differ from domain to domain.

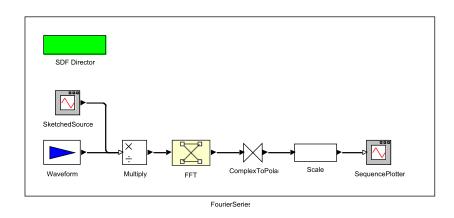

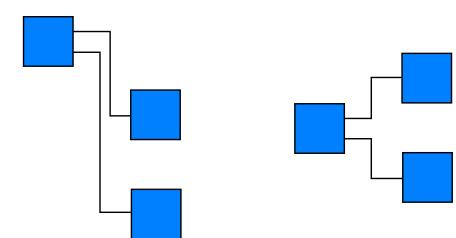

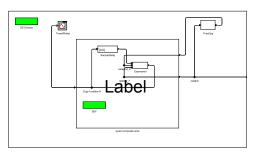

The diagram type relevant to this thesis are *data flow diagrams*. With data flow diagrams, the system is represented by components, usually called actors, that process data and links that define how data is distributed between the actors. This distribution is also called the data flow. Data flow diagrams themselves were subject to a lot of research work in computer science over the last decades, and may have a different behaviour or semantics, depending on the definitions [Kah74, LM87]. An example for a data flow diagram is given in Figure 1.2, where the Fourier transformation of a waveform is computed and plotted.

As the name of this diagram type suggest, an important part of the drawings is the flow of the data. Hence, one goal of an automatic layout approach would be to arrange the drawing in a way that emphasizes the flow of data, resulting in a diagram that is easy to follow. An approach which deals with exactly this problem is the *hierarchical* or *layered* layout approach.

To be able to cope with a complex task such as automatic layout, algorithms are

<sup>&</sup>lt;sup>1</sup>http://purl.org/goodrelations/

### 1.1. Related Work

**Figure 1.2.** A data flow diagram from the Ptolemy II modelling tool [EJL<sup>+</sup>03], showing the computation of a Fourier series.

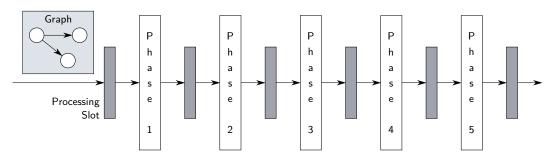

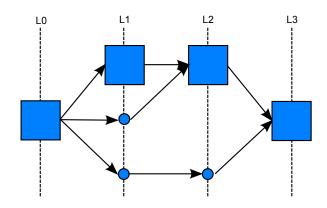

usually split into several subtasks or phases. One such phase of the layered layout approach is called *node placement*, which computes the vertical coordinates of actors given a horizontal arrangement computed by a previous phase. This subtask will be dealt with in this thesis.

Another subtask can be the placement of diagram annotations or *labels*. Usually, label placement is applied as post-processing, taking a laid out diagram and fitting the labels into the drawing. In this thesis, approaches are explored that integrate label placement into the actual layout algorithm, resulting in an easier placement due to the ability to explicitly reserve space for the labels.

To give a better idea of the scientific environment and other work on the topics of this thesis, the following section will present related work, investigate the groundwork for the approaches of this thesis, and distinguish other approaches that might look similar at a first glance.

### 1.1 Related Work

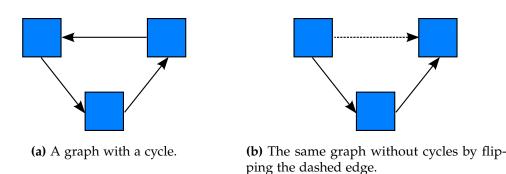

An approach for drawing directed, acyclic graphs, known as the hierarchical or layered approach, was proposed by Sugiyama, Tagawa, and Toda [STT81]. They split the problem of graph drawing into several sub problems to make it more manageable. The general idea of sorting vertices into layers that are placed below or above each other is realized in three steps. In the first step, the set of vertices is partitioned into layers. After that, the order of the vertices inside every layer

#### 1. Introduction

is changed such that the connections between the vertices of any two consecutive layers produce as few crossings as possible. In a final phase, the horizontal position of every vertex is determined, as the vertical position is indicated by the layering. As this thesis deals with vertex positioning (also referred to as node placement), the work of Sugiyama et al. is groundwork for it and implemented in an algorithm based on the Sugiyama approach that will be presented later in this section.

Several approaches to the node placement sub task were investigated. An approach by Sander uses the concept of *linear segments*, grouping vertices that are placed on a straight line [San96]. Linear segments are used mainly to make sure that edges spanning multiple layers are drawn straightly, while connections between actors are neglected.

A similar but more complex approach which creates larger vertex groups is proposed by Buchheim et al. [BJL01]. In the beginning, a virtual placement is created by placing vertices leftmost or rightmost. The average of this placement is used for thoroughly traversing the graph layer-wise until optimal sequences of vertices are found. With this, every edge has at most two bends if a straightforward edge drawing is used. Compared to the following approach, this approach consists of complex algorithms with larger run times.

A third approach is proposed by Ulrik Brandes and Boris Köpf [BK02]. Again, vertices are grouped into larger units called *blocks* whose vertices are placed on a straight line. This approach can be seen as being in the middle of the two other approaches. The blocks can also consist of vertices and edges, but are created in a best effort manner by traversing the graph in four directions, contrary to the complex sequencing of Buchheim. The approach of this thesis bases on the approach by Brandes and Köpf by extending it, especially by adding support for vertex sizes and connection points.

For the evaluation of results, a method for quantifying the quality of a layout is necessary. Basic aesthetics criteria were presented by Sugiyama et al. alongside with their layout approach.

A work that focusses on aesthetics of drawn graphs is presented by Helen Purchase [Pur02]. She presents aesthetics criteria that can be applied to decide on the quality of a graph drawing.

In terms of label placement, the root of the placement problems is found outside of the domain of computer science. The first approaches on this field were connected to cartography, dealing with the placement of city names or other landmarks on drawn maps.

First approaches to an automatic placement of labels in cartography were

investigated by Pinhas Yoeli and Eduard Imhof [Yoe72, Imh75]. They laid the foundation for most placement algorithms by introducing the approach of defining a set of candidate positions for each label, preferably close to the labeled element, and a set of quality rules to guide the selection of the best of the offered candidate positions.

While computer science has developed algorithms for a good cartographic labeling, the introduction of graphical modelling and layout algorithms created a new set of problems in the domain of graph labeling. Konstantinos Kakoulis and Ioannis Tollis did a lot of research in this area and developed algorithms for different labeling problems in graph drawing, most notably node label placement and edge label placement as a post-processing on an already drawn graph [KT03]. They apply the candidate position approach to the different placement problems. Label placement in this thesis is addressed in a similar way. However, instead of performing a post-processing on an already laid out graph, the placement is incorporated into the layout, thus adding the ability to explicitly reserve space for the labels.

An interesting approach to label placement is presented by Pak Wong et al. [WMP<sup>+</sup>05]. Instead of placing edge labels close to an edge, they use the label itself to represent the edge. Although this is certainly a creative idea, the practical usage is questionable since readability, especially with respect to edge crossings, is then an issue.

In the *dot* layout algorithm by Gansner et al., label placement is also incorporated into the layout algorithm and space for edge labels is reserved by modifying the edge routing [GKN02]. The label is then placed next to the center of an edge and can also be connected to the corresponding edge by a dashed line. This is a rather simple and inflexible method, thus a different approach is chosen in this thesis.

Castelló et al. have published research on label placement in a layered layout approach for state charts [CMT01]. For a feasible placement of edge labels, they introduce sub layers which are placed between the regular layers. The space created by these sub layers is used for the placement of edge labels. While this is a good approach for state charts where edge labels usually follow a uniform structure, some problems occur in data flow diagrams. Not every connection has a label, and the labels may be structured differently, resulting in having to reserve enough space for the largest label. The following approach, that also uses virtual structures introduced by the layout algorithm, such as dummy vertices and layers, might be a better compromise.

Although Eiglsperger et al. worked on label placement in an orthogonal layout

### 1. Introduction

instead of a layered layout, one of their ideas can be used in the context of layered layout as well. In orthogonal layouts, dummy vertices that are not part of the original drawing are used to create ninety degree angles. Eiglsperger et al. use these dummy vertices to save space for labels [EKS03]. A similar approach is used in the context of layered layouts in this thesis.

In the environment of Kiel Integrated Environment for Layout Eclipse Rich Client (KIELER), a framework whose goal it is to improve the pragmatics of graphical modelling [FvH10], several researchers investigated and implemented layout algorithms for data flow diagrams. Most notable for the topics dealt with in this thesis is the work of Miro Spönemann and Christoph Daniel Schulze. Spönemann compared hierarchical and orthogonal layout approaches for their use in data flow diagrams, resulting in a modified implementation of Sugiyama's approach with feasible results [Spö09]. Schulze improved this implementation, especially with respect to edge connection points [Sch11]. Additionally, he restructured the algorithm to be more adaptive, allowing to introduce sub tasks between and after the main phases of the algorithm.

### **1.2 Research Goals**

As mentioned in the previous section, the contributions of this thesis will be implemented into the KIELER Layout Algorithms (KLay) Layered layout algorithm. As this thesis consists of two separate problems in the same layout algorithm, the research goals for this thesis are presented in two sections.

#### 1.2.1 Improving Node Placement

The node placement problem is a sub task of the layered layout approach. It decides on vertical positions of diagram elements, after a horizontal ordering was determined by an earlier phase. While it is not that important for the understanding of node placement, keep in mind that the final horizontal position is computed by the last sub task of the algorithm.

The current implementation in the context of KLay Layered has algorithms for each of the sub tasks of the layered layout approach. However, these algorithms are heuristics and may not always produce an optimal result with respect to certain criteria. As Christoph Daniel Schulze also pointed out in his diploma thesis, the results of the current node placement algorithms are not satisfying in some cases,

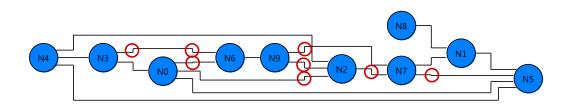

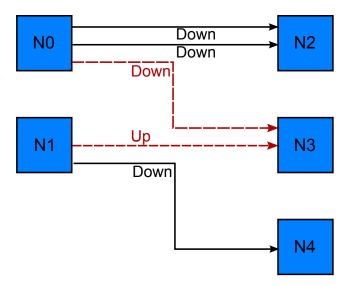

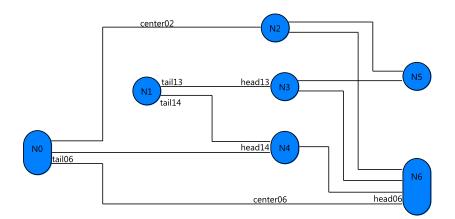

**Figure 1.3.** An example result of KLay Layered, with edge bends marked of which at least some may be avoided.

especially because unnecessary edge bends are introduced [Sch11]. An example for that can be seen in Figure 1.3.

The first goal of this thesis is the improvement of node placement. A different approach to node placement has to be found, focussing on the straight drawing of edges. As the main domain of applications are data flow diagrams, connections in diagrams will be drawn orthogonally, meaning that all angles in the drawings are ninety degrees. This results in many edge bends if connection points of edges are not assigned the same vertical coordinate. Thus, vertical coordinates have to be found in which as many connection points as possible are on the same level.

While a better node placement behaviour with respect to edge bends is the main goal of this thesis, other, connected new features may be introduced as sub goals. A sub goal could for example be the development of a priority mechanism which tries to give certain edges priority over others when it comes to deciding which edges to draw straightly.

### 1.2.2 Implementing Label Placement

The goals in terms of label placement are more open. This is, because there is no real label placement included in the current implementation of KLay Layered, resulting in a wide field of possible goals and approaches.

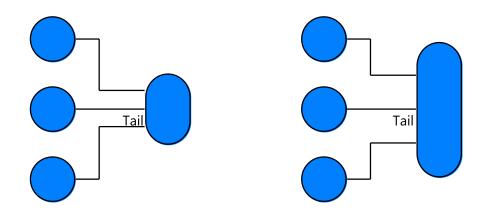

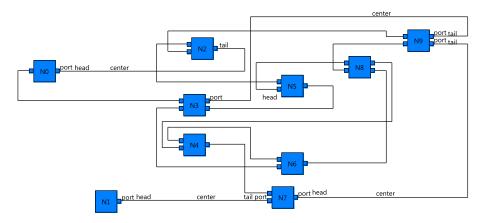

Label placement can refer to all kinds of annotations or text fields in a graph. Normally, these annotations are connected to certain elements of a diagram, for example, connectors. So the general task of label placement is to draw these annotations close to their connected elements. Furthermore, the labels should be drawn well away from other elements, to prevent any kind of overlapping or ambiguity as to which elements a label belongs to.

To keep the goals comprehensible, this wide field has to be reduced to a certain

1. Introduction

subset. A lot of work has already been done in terms of placing labels as a postprocessing step. Thus, the goal of this thesis is an investigation of placement approaches that can be integrated into a layout algorithm such that the placement is easier and better, because the whole layout can be changed to reserve enough space for a good label placement.

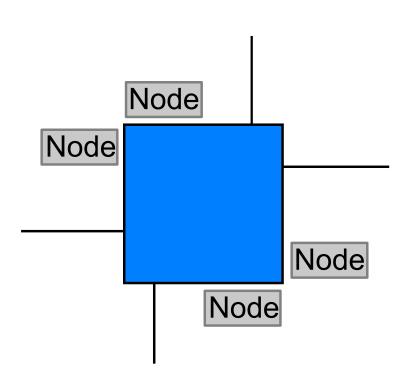

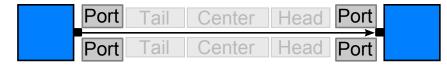

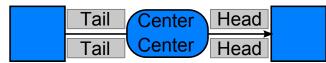

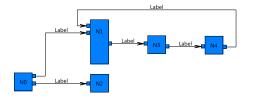

### 1.3 Overview